# Aspects of Code Generation and Data Transfer Techniques for Modern Parallel Architectures

zur Erlangung des akademischen Grades eines

# Doktors der Ingenieurwissenschaften / Doktors der Naturwissenschaften

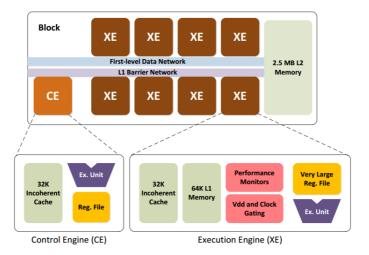

der KIT-Fakultät für Informatik des Karlsruher Instituts für Technologie (KIT)

# vorgelegte Dissertation

von

#### **Manuel Mohr**

aus Heilbronn

Tag der mündlichen Prüfung: tbd

Erster Gutachter: Prof. Dr.-Ing. Gregor Snelting

Zweiter Gutachter: Prof. Dr.-Ing. Jürgen Teich

Dritter Gutachter: Prof. Dr. rer. nat. Sebastian Hack

## Eidesstattliche Erklärung

Hiermit erkläre ich an Eides statt, die vorliegende Dissertation selbstständig und nur unter Zuhilfenahme der ausgewiesenen Hilfsmittel angefertigt zu haben. Sämtliche Stellen der Arbeit, die im Wortlaut oder dem Sinn nach anderen gedruckten oder im Internet verfügbaren Werken entnommen sind, habe ich durch genaue Quellenangaben kenntlich gemacht. Ich erkläre außerdem, dass die Dissertation weder in gleicher noch in ähnlicher Form bereits in einem anderen Prüfungsverfahren vorgelegen hat.

Karlsruhe, den 14. Dezember 2017

Manuel Mohr

#### **Affidavit**

I hereby confirm that the dissertation at hand is the result of my own work. All used or quoted sources and materials are listed and specified in the dissertation. Furthermore, I confirm that this dissertation has not yet been submitted as part of another examination process neither in identical nor in similar form.

Karlsruhe, December 14, 2017

Manuel Mohr

# **Contents**

| Co | nteni | IS      |                                 | V  |

|----|-------|---------|---------------------------------|----|

| 1. | Intro | ductio  | n                               | 1  |

|    | 1.1.  | Contri  | ibutions                        | 6  |

|    | 1.2.  | Struct  | ure                             | 9  |

|    | 1.3.  | Notati  | on and Conventions              | 10 |

|    | 1.4.  | List of | Publications                    | 10 |

| 2. | Non   | -Cache  | -Coherent Architectures         | 13 |

|    | 2.1.  | A Taxo  | onomy of Parallel Architectures | 13 |

|    |       | 2.1.1.  | Memory Organization             | 14 |

|    |       | 2.1.2.  | Communication Model             | 14 |

|    |       | 2.1.3.  | Typical Combinations            | 16 |

vi Contents

|    | 2.2. | Cache   | Coherence                                      | 17 |

|----|------|---------|------------------------------------------------|----|

|    |      | 2.2.1.  | Separating Coherence from Consistency          | 19 |

|    |      | 2.2.2.  | Implementation                                 | 21 |

|    | 2.3. | Hardv   | vare Architecture                              | 30 |

|    |      | 2.3.1.  | Examples of Non-Cache-Coherent Architectures . | 33 |

|    | 2.4. | Progra  | amming Model                                   | 40 |

|    |      | 2.4.1.  | Parallel Programming Models                    | 41 |

|    |      | 2.4.2.  | Shared-Memory Programming Model                | 43 |

|    |      | 2.4.3.  | Message Passing                                | 49 |

|    |      | 2.4.4.  | The PGAS Model                                 | 53 |

| 3. | Inva | sive Co | omputing                                       | 57 |

|    | 3.1. | The In  | avasive Paradigm                               | 58 |

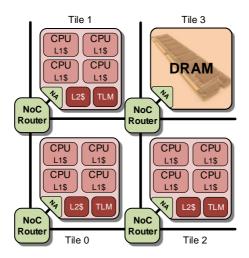

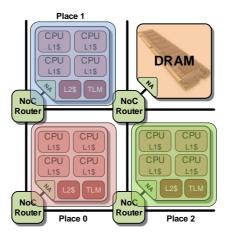

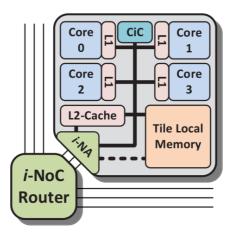

|    | 3.2. | Hardv   | vare Architecture                              | 60 |

|    |      | 3.2.1.  | Related Work                                   | 62 |

|    | 3.3. | Opera   | ting System                                    | 63 |

|    |      | 3.3.1.  | Related Work                                   | 66 |

|    | 3.4. | Progra  | amming Language                                | 68 |

|    |      | 3.4.1.  | Shared-Memory Parallelism                      | 70 |

|    |      | 3.4.2.  | Distributed-Memory Parallelism                 | 72 |

|    |      | 3.4.3.  | Related Work                                   | 74 |

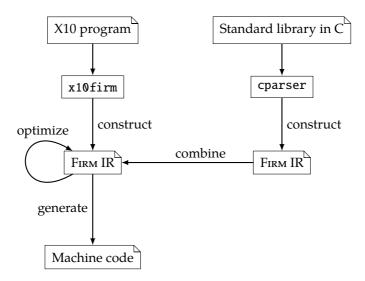

|    | 3.5. | Comp    | iler                                           | 75 |

|    |      | 3.5.1.  | Compilation of Generic Classes and Methods     | 76 |

|    |      | 3.5.2.  | Handling of Native Methods                     | 78 |

|    | 3.6. | Hardv   | vare Prototype                                 | 80 |

Contents vii

| 4. | Com  | piling                     | X10 to Invasive Architectures            | 83  |  |  |

|----|------|----------------------------|------------------------------------------|-----|--|--|

|    | 4.1. | Intra-                     | Intra-Tile Parallelism                   |     |  |  |

|    | 4.2. | Inter-7                    | Tile Parallelism                         | 89  |  |  |

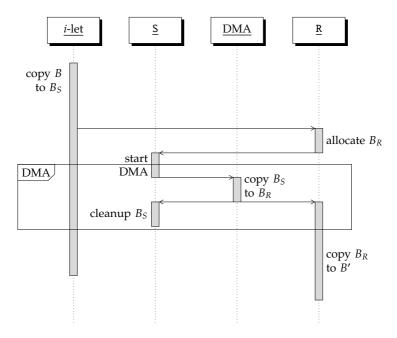

|    | 4.3. | Block-Based Data Transfers |                                          |     |  |  |

|    |      | 4.3.1.                     | Using TLM                                | 93  |  |  |

|    |      | 4.3.2.                     | Using Off-Chip Memory                    | 97  |  |  |

|    |      | 4.3.3.                     | Related Work                             | 99  |  |  |

|    |      | 4.3.4.                     | Implementation on the Hardware Prototype | 101 |  |  |

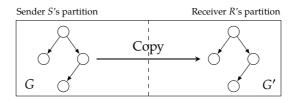

|    | 4.4. | Transf                     | erring Pointered Data Structures         | 108 |  |  |

|    |      | 4.4.1.                     | Serialization-Based Approaches           | 114 |  |  |

|    |      | 4.4.2.                     | Cloning-Based Approaches                 | 117 |  |  |

|    |      | 4.4.3.                     | Related Work                             | 122 |  |  |

|    |      | 4.4.4.                     | Implementation on the Hardware Prototype | 125 |  |  |

|    | 4.5. | Hardv                      | vare Support                             | 128 |  |  |

|    |      | 4.5.1.                     | Design Space                             | 129 |  |  |

|    |      | 4.5.2.                     | Concept and Implementation               | 131 |  |  |

|    |      | 4.5.3.                     | Related Work                             | 134 |  |  |

|    | 4.6. | Evalua                     | ation                                    | 135 |  |  |

|    |      | 4.6.1.                     | Setup                                    | 135 |  |  |

|    |      | 4.6.2.                     | Establishing an Evaluation Environment   | 137 |  |  |

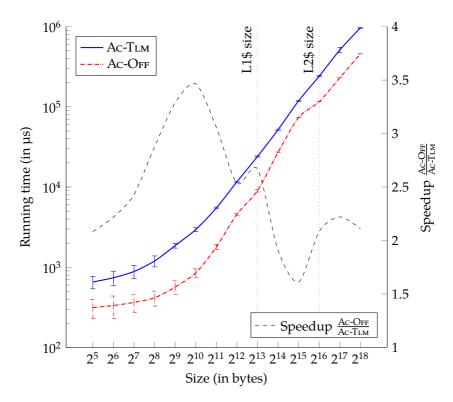

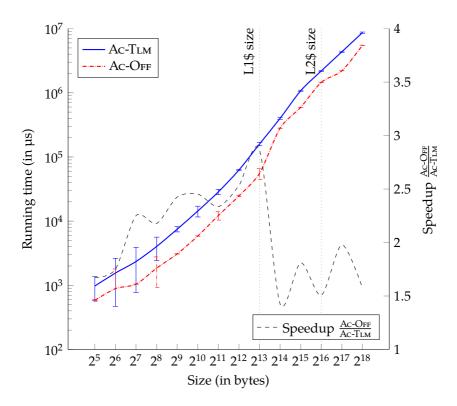

|    |      | 4.6.3.                     | Block-Based Data Transfers               | 140 |  |  |

|    |      | 4.6.4.                     | Transfers of Pointered Data Structures   | 142 |  |  |

|    |      | 4.6.5.                     | Hardware Overhead                        | 159 |  |  |

|    |      | 4.6.6.                     | Threats to Validity                      | 162 |  |  |

|    | 4.7. | Relation                   | on to Invasive X10                       | 164 |  |  |

viii Contents

| 5. | Cod  | e Gene | ration with Permutation Instructions         | 171 |

|----|------|--------|----------------------------------------------|-----|

|    | 5.1. | Introd | luction                                      | 176 |

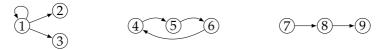

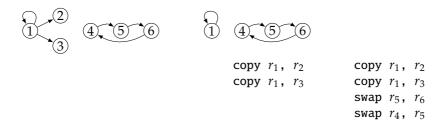

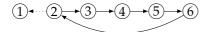

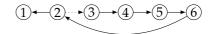

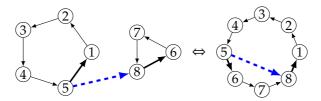

|    |      | 5.1.1. | Parallel Copies and Register Transfer Graphs | 176 |

|    |      | 5.1.2. | Permutation Instructions                     | 182 |

|    | 5.2. | Hardv  | vare Implementation                          | 187 |

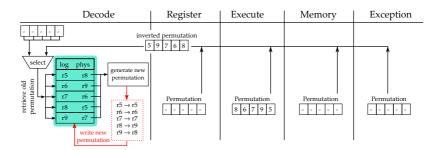

|    |      | 5.2.1. | Fundamental Pipeline Modifications           | 187 |

|    |      | 5.2.2. | Exception Handling                           | 191 |

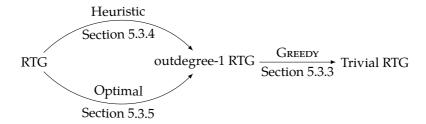

|    | 5.3. | Code   | Generation                                   | 194 |

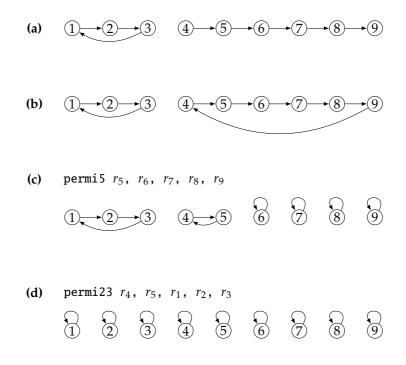

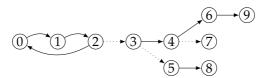

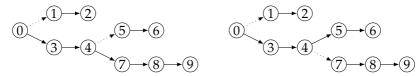

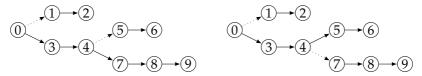

|    |      | 5.3.1. | Implementing RTGs on Regular Machines        | 195 |

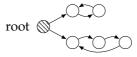

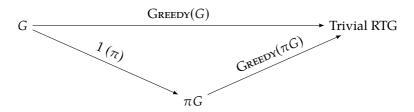

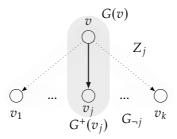

|    |      | 5.3.2. | Reformulation as a Graph Problem             | 198 |

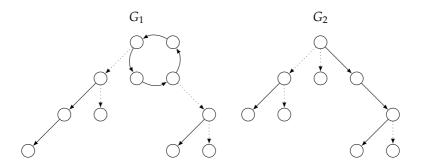

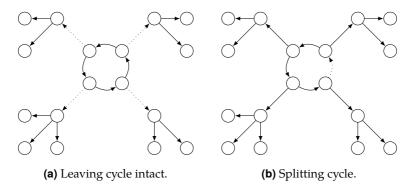

|    |      | 5.3.3. | Optimal Shuffle Code for Outdegree-1 RTGs    | 204 |

|    |      | 5.3.4. | A Heuristic for Finding Copy Sets            | 214 |

|    |      | 5.3.5. | Finding Optimal Copy Sets                    | 218 |

|    |      | 5.3.6. | Related Work                                 | 232 |

|    | 5.4. | Evalua | ation                                        | 234 |

|    |      | 5.4.1. | Setup                                        | 234 |

|    |      | 5.4.2. | Register-Transfer-Graph Properties           | 237 |

|    |      | 5.4.3. | Heuristic and Optimal Code Generation        | 238 |

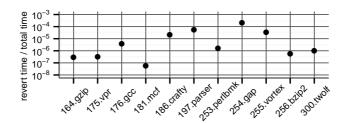

|    |      | 5.4.4. | Compilation Time                             | 240 |

|    |      | 5.4.5. | Code Quality                                 | 242 |

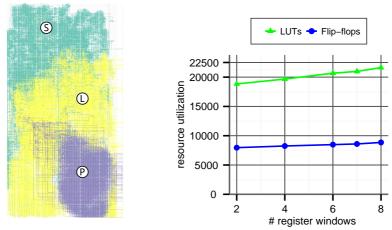

|    |      | 5.4.6. | Hardware Overhead                            | 250 |

|    |      | 5.4.7. | Threats to Validity                          | 252 |

|    | 5.5. | Gener  | alization                                    | 255 |

|    |      | 5.5.1. | Out-of-Order Execution                       | 255 |

|    |      | 5.5.2. | Implementing Permutation Instructions        | 258 |

Contents ix

| 6.  | Conclusion and Future Work                                          | 263 |

|-----|---------------------------------------------------------------------|-----|

| Α.  | Appendix                                                            | 269 |

|     | A.1. Recommendations for Invasive Architectures $\ \ldots \ \ldots$ | 269 |

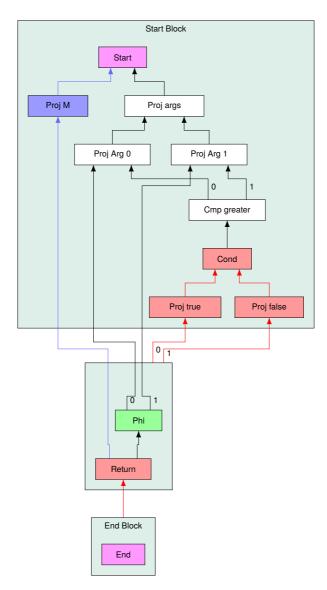

|     | A.2. The Intermediate Representation Firm $\dots \dots \dots$       | 271 |

|     | A.3. $k$ -Shuffle Code Generation is NP-complete                    | 274 |

|     | A.3.1. Complexity                                                   | 274 |

|     | A.3.2. Approximation Algorithm                                      | 275 |

| В.  | Software Artifacts                                                  | 277 |

| C.  | Curriculum Vitae                                                    | 279 |

| Lis | st of Figures                                                       | 281 |

| Lis | st of Tables                                                        | 287 |

| Inc | lex                                                                 | 319 |

**Ernest Hemingway**

#### **Abstract**

The focus of hardware architecture development has shifted from striving for ever higher clock frequencies towards incorporating an ever increasing number of cores on a single chip. A high number of cores makes it possible to offer a mixture of weak and strong cores, and even specialized cores with completely different instruction sets. This makes development for such a heterogeneous platform challenging and requires adequate support by tools, such as compilers. Besides their core structure, there is a second dimension to these architectures: memory. A major obstacle to scalability regarding the memory hierarchy of many-core platforms is maintaining global cache coherence. Hardware coherence protocols either scale poorly, or are complex and often suffer from performance and power overheads. Abandoning global cache coherence is a radical solution to this problem. However, efficiently mapping programming models to hardware with relaxed guarantees is challenging. In this dissertation, we make contributions to compilation techniques targeting both dimensions of modern parallel architectures: memory and core structure.

The first part of this dissertation concerns data transfer techniques for non-cache-coherent architectures. Such non-cache-coherent shared-memory

xii Contents

architectures provide a shared physical address space, but do not implement hardware-based coherence between all caches of the system. Logically partitioning the shared memory offers a safe way of programming such a platform. In general, this creates the need to copy data between memory partitions.

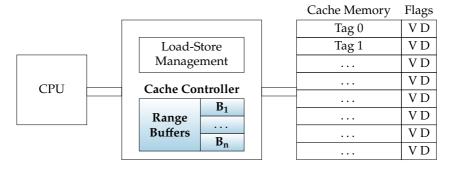

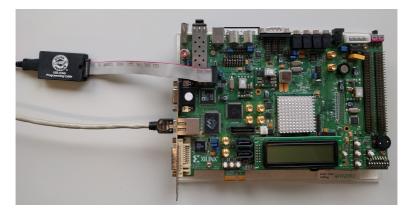

We study the compilation to invasive architectures, a family of non-cache-coherent many-core architectures. We investigate the efficient implementation of data transfers for both simple and complex data structures on these architectures. Specifically, we propose a novel approach to copy complex pointered data structures without the need for serialization. To this end, we generalize object cloning to work in the presence of non-coherent caches by extending object cloning with compiler-directed automatic software-managed coherence. We present implementations of multiple data transfer techniques in an existing compiler and runtime system. We extensively evaluate these implementations on an FPGA-based prototype of an invasive architecture. Finally, we propose adding hardware support for range-based cache operations, and describe and evaluate possible implementations and overheads.

The second part of this dissertation concerns code generation techniques to accelerate shuffle code by using permutation instructions. Shuffle code arises during register allocation, where the compiler maps program variables to machine registers. The compiler may introduce shuffle code, consisting of copy and swap operations, to transfer data between registers. Depending on the quality of register allocation and the number of available registers, a large amount of shuffle code may be generated.

We propose to speed up the execution of shuffle code by using permutation instructions that arbitrarily permute the contents of small sets of registers in one clock cycle. To show the feasibility of this idea we first present an extension of an existing RISC instruction set with permutation instructions. We then describe how to implement the proposed permutation instructions in an existing RISC architecture. Subsequently, we develop two code generation schemes that exploit permutation instructions to implement shuffle code: a fast heuristic and a dynamic-programming-based approach. We formally prove quality and correctness properties of both approaches and show the latter approach to be optimal. In the following, we implement both code generation algorithms in a compiler and extensively evaluate

Contents xiii

and compare their code quality using a standardized benchmark suite. We first measure precise dynamic instruction counts, which we then validate by measuring running times on an FPGA-based prototype implementation of the proposed RISC architecture with permutation instructions. Finally, we argue that permutation instructions are cheap to implement on modern out-of-order architectures that already support register renaming.

Lehrstuhlweisheit, nach Rubino Geiß

### Zusammenfassung

Im Bereich der Prozessorarchitekturen hat sich der Fokus neuer Entwicklungen von immer höheren Taktfrequenzen hin zu immer mehr Kernen auf einem Chip verschoben. Eine hohe Kernanzahl ermöglicht es unterschiedlich leistungsfähige Kerne anzubieten, und sogar dedizierte Kerne mit speziellen Befehlssätzen. Die Entwicklung für solch heterogene Plattformen ist herausfordernd und benötigt entsprechende Unterstützung von Entwicklungswerkzeugen, wie beispielsweise Übersetzern. Neben ihrer heterogenen Kernstruktur gibt es eine zweite Dimension, die die Entwicklung für solche Architekturen anspruchsvoll macht: ihre Speicherstruktur. Die Aufrechterhaltung von globaler Cache-Kohärenz erschwert das Erreichen hoher Kernzahlen. Hardwarebasierte Cache-Kohärenz-Protokolle skalieren entweder schlecht, oder sind kompliziert und führen zu Problemen bei Ausführungszeit und Energieeffizienz. Eine radikale Lösung dieses Problems stellt die Abschaffung der globalen Cache-Kohärenz dar. Jedoch ist es schwierig, bestehende Programmiermodelle effizient auf solch eine Hardware-Architektur mit schwachen Garantien abzubilden.

Der erste Teil dieser Dissertation beschäftigt sich Datentransfertechniken für nicht-cache-kohärente Architekturen mit gemeinsamem Speicher. xvi Contents

Diese Architekturen bieten einen gemeinsamen physikalischen Adressraum, implementieren aber keine hardwarebasierte Kohärenz zwischen allen Caches des Systems. Die logische Partitionierung des gemeinsamen Speichers ermöglicht die sichere Programmierung einer solchen Plattform. Im Allgemeinen erzeugt dies die Notwendigkeit Daten zwischen Speicherpartitionen zu kopieren.

Wir untersuchen die Übersetzung für invasive Architekturen, einer Familie von nicht-cache-kohärenten Vielkernarchitekturen. Wir betrachten die effiziente Implementierung von Datentransfers sowohl einfacher als auch komplexer Datenstrukturen auf invasiven Architekturen. Insbesondere schlagen wir eine neuartige Technik zum Kopieren komplexer verzeigerter Datenstrukturen vor, die ohne Serialisierung auskommt. Hierzu verallgemeinern wir den Objekt-Klon-Ansatz mit übersetzergesteuerter automatischer software-basierter Kohärenz, sodass er auch im Kontext nicht-kohärenter Caches funktioniert. Wir präsentieren Implementierungen mehrerer Datentransfertechniken im Rahmen eines existierenden Übersetzers und seines Laufzeitsystems. Wir führen eine ausführliche Auswertung dieser Implementierungen auf einem FPGA-basierten Prototypen einer invasiven Architektur durch. Schließlich schlagen wir vor, Hardwareunterstützung für bereichsbasierte Cache-Operationen hinzuzufügen und beschreiben und bewerten mögliche Implementierungen und deren Kosten.

Der zweite Teil dieser Dissertation befasst sich mit der Beschleunigung von Shuffle-Code, der bei der Registerzuteilung auftritt, durch die Verwendung von Permutationsbefehlen. Die Aufgabe der Registerzuteilung während der Programmübersetzung ist die Abbildung von Programmvariablen auf Maschinenregister. Während der Registerzuteilung erzeugt der Übersetzer Shuffle-Code, der aus Kopier- und Tauschbefehlen besteht, um Werte zwischen Registern zu transferieren. Abhängig von der Qualität der Registerzuteilung und der Zahl der verfügbaren Register kann eine große Menge an Shuffle-Code erzeugt werden.

Wir schlagen vor, die Ausführung von Shuffle-Code mit Hilfe von neuartigen Permutationsbefehlen zu beschleunigen, die die Inhalte von einigen Registern in einem Taktzyklus beliebig permutieren. Um die Machbarkeit dieser Idee zu demonstrieren, erweitern wir zunächst ein bestehendes RISC-Befehlsformat um Permutationsbefehle. Anschließend beschreiben

Contents xvii

wir, wie die vorgeschlagenen Permutationsbefehle in einer bestehenden RISC-Architektur implementiert werden können. Dann entwickeln wir zwei Verfahren zur Codeerzeugung, die die Permutationsbefehle ausnutzen, um Shuffle-Code zu beschleunigen: eine schnelle Heuristik und einen auf dynamischer Programmierung basierenden optimalen Ansatz. Wir beweisen Qualitäts- und Korrektheitseingeschaften beider Ansätze und zeigen die Optimalität des zweiten Ansatzes. Im Folgenden implementieren wir beide Codeerzeugungsverfahren in einem Übersetzer und untersuchen sowie vergleichen deren Codequalität ausführlich mit Hilfe standardisierter Benchmarks. Zunächst messen wir die genaue Zahl der dynamisch ausgeführten Befehle, welche wir folgend validieren, indem wir Programmlaufzeiten auf einer FPGA-basierten Prototypimplementierung der um Permutationsbefehle erweiterten RISC-Architektur messen. Schließlich argumentieren wir, dass Permutationsbefehle auf modernen Out-Of-Order-Prozessorarchitekturen, die bereits Registerumbenennung unterstützen, mit wenig Aufwand implementierbar sind.

Hofstadter's Law: It always takes longer than you expect, even when you take into account Hofstadter's Law.

Douglas Hofstadter

## **Acknowledgments**

First, I wish to thank my advisor Prof. Gregor Snelting for his support and the opportunity to pursue my own interests without pressure. I also thank him for shielding me and his whole group from the many adversities of academic life, such as the need to secure a steady stream of money. He provided an environment where it was possible to concentrate on research, on building efficient and robust software, as well as on excellence in teaching, which is a luxury one becomes accustomed to far too easily. Next, I would like to thank Prof. Jürgen Teich for reviewing this dissertation. I also thank him for founding the research project Invasive Computing, which taught me a great deal about hardware, software, the many things that can go wrong between them—and how great it is when they finally work together. The first part of this dissertation would not have been possible without this research project. Moreover, I want to thank Prof. Sebastian Hack for serving as the third reviewer of this dissertation. I also thank him for leaving an inconspicuous footnote in his dissertation, which ultimately gave rise to the second part of this work.

Next, I have to thank the (former and current) machine code connoisseurs from the compiler group in Karlsruhe, namely Matthias Braun, Sebastian

xx Contents

Buchwald, Andreas Fried, and Andreas Zwinkau. I especially thank my former office inmate Matthias Braun for being a walking encyclopedia of Firm and x86 peculiarities and for sharing his knowledge with me. Furthermore, I thank Sebastian Buchwald for his tireless commitment to correctness and clarity of expression in both code and written text. And also for removing all trailing whitespace¹. I thank Andreas Zwinkau for joining me in the quest to bring the invasive prototype system to life while at the same time keeping me up to date on every development in the world of programming languages. Lastly, I thank Andreas Fried for being a very knowledgable office mate, and for creating the nerdiest and most difficult crossword puzzle I ever failed to solve. All compiler constructors were always available for help and technical discussions. Without them, countless hours of staring at Firm graphs and assembly dumps would have been much more boring.

However, our group consisted of more than the pointer arithmeticians in the compiler group. Thus, I also thank all my context-sensitive colleagues from the JOANA group, namely Simon Bischof, Jürgen Graf, Martin Hecker, and Martin Mohr. In particular, I thank Simon Bischof for finding an embarrassing number of bugs in our compiler lab reference compiler. I thank Jürgen Graf for annual barbecues on his panorama terrace and being a close (pun intended) friend. I thank Martin Hecker for his dedication to improving the quality of our teaching material and for regularly destroying half-baked or unfair exam question proposals. And I thank Martin Mohr for his quirky humorous remarks and his love for everything at the bottom of the movie barrel. May all your wishes happen in parallel.

Moreover, I thank all side-effect-free purists from our automated theorem proving group, namely Joachim Breitner, Andreas Lochbihler, Denis Lohner, Sebastian Ullrich, and Maximilian Wagner. I thank Joachim Breitner for producing new ideas faster than I could follow the previous ones, and for proving that days do have more than 24 hours for some people. I thank "Altgesell" Andreas Lochbihler for taking me under his wing back when I started as a doctoral researcher, and also for letting all our dissertations seem short in comparison. I thank Denis Lohner for his outstanding organizational skills and for his arcane knowledge of AFS and other technological oddities in our infrastructure. Lastly, I thank Sebastian

<sup>&</sup>lt;sup>1</sup>I broke one ligature in this section on purpose, did you spot it?

Contents xxi

Ullrich and Maximilian Wagner for humiliating us and our compiler lab reference compiler in front of everyone, and for convincing me that it is possible to write beautiful Scala code.

Technically, I ought to mention everyone I met via the Invasive Computing project, but this list would be too long. Hence, I have to pick some subset and apologize in advance to everyone I do not mention. Thanks to the operating systems group in Erlangen, namely Gabor Drescher, Christoph Erhardt, Sebastian Maier, Benjamin Oechslein, Jens Schedel, and Florian Schmaus for joining us in valiantly defending the system-software layer against evil feature-request deniers from the hardware down below and against blissfully ignorant application developers from above. Project C1 set the bar high for system software quality, just like it should be. I also thank Lars Bauer and Artjom Grudnitsky for realizing the slightly crazy register permutation idea and answering all my stupid questions about hardware. And I thank Stephanie Friederich, Jan Heißwolf, Sven Rheindt, and Aurang Zaib for bringing our hardware platform to life. Special thanks go to Sven Rheindt, who exhumed an ancient hardware design from its grave in a decommissioned Subversion repository and added some new functionality to it, just so I could improve my evaluation. Without people like the ones I just mentioned, who went the extra mile and sometimes traded fewer publications for more fixed bugs, the Invasive Computing project would not have come as far as it did. They all made the countless hours of fighting Scheinzwerge and Heisenbugs much more worthwhile.

Furthermore, I thank Carsten Tradowsky for throwing student after student at our project of extending hardware with range-based cache operations. He mastered the art of delegating tasks.

I thank Ignaz Rutter for his tremendous help with formalizing and investigating the theoretical aspects of shuffle-code generation. Back in May 2012, I innocently walked into his office with my little problem of generating shuffle code, expecting him to point me to some existing paper or book chapter. Somehow, a few months later, I had pages and pages of lemmas and proofs, and also quite some trouble still recognizing my own problem. It was a pleasure witnessing him working his magic while being able to contribute a bit of my own. I also thank him for initiating weekly Ricochet Robots rounds years ago.

xxii Contents

Of course, I must mention all students who contributed to software or hardware projects that I used. One of the luxuries of working at a university is the large pool of talented and highly motivated students I could draw from. Hence, I thank Eduard Frank, Jonas Haag, Christoph Jost, Tobias Kahlert, Tobias Modschiedler, Julian Oppermann, Tobias Rapp, Bernhard Scheirle, Martin Seidel, and Philipp Serrer for their contributions.

I also thank all hard-working proof readers, who ploughed through hundreds of pages and found issues both small and large. Namely my helpers were Sebastian Buchwald, Christoph Erhardt, Andreas Fried, Marina Mohr, Martin Mohr, Maximilian Wagner, and Andreas Zwinkau.

Moreover, I thank my parents as well as my sister Marina for their unconditional support of whatever decision I made and whatever task I set my mind on. They always encouraged me to pursue my interests and not to be afraid of taking on challenges. I especially thank my father for denying me my wish for a VTech learning computer and instead putting a real PC into my room; something I assume very few nine year olds had at that time. This sparked my interest in computers and programming and I benefit from this decision to this day.

Finally, I thank Eva for supporting and enduring me during the past years. In her, I have always found both an attentive listener as well as a keen observer. I highly value her advice, as she is right more often than I like to admit. While working on this pamphlet, I have read my share of dissertations in search of inspiration and almost everyone acknowledges the many ups and downs that working in solitude on a document of such size entails. Little did I know how high the ups can be—and how deep the downs. However, I could always count on her support, for which I was and am extremely grateful.

After such an introduction, I can hardly wait to hear what I'm going to say.

Evelyn Anderson

1

#### Introduction

During the last decade, the computer architecture landscape has changed dramatically. Up until circa 2005, processor designers focused on improving single-thread performance. Moore's Law [Mac11] provided an ongoing miniaturization of transistors, enabling more logic per chip area, while at the same time Dennard scaling [Den+74] allowed to operate these transistors at decreasing voltages and currents.

These advances in chip manufacturing enabled the three main drivers behind faster execution of sequential code: (i) higher clock speeds, i.e., finishing more clock cycles in the same amount of time, (ii) larger caches, i.e., the ability to keep more data close to the core for fast access, and (iii) architectural improvements, i.e., doing more work per clock cycle. The architectural improvements mainly aimed at exploiting instruction-level parallelism (ILP) [HP11, chapter 2]. This included techniques such as prediction of branches in the control flow; dynamic scheduling of instruction streams (also known as out-of-order execution); and speculative execution. Overall, this led to increasingly complex processors.

Then, around 2005, Dennard scaling started to break down. Now it was no longer possible to lower transistor voltages and currents to compensate for increased power usage due to higher frequencies. Hence, clock frequencies started to stagnate while Moore's Law still continued to

2 1. Introduction

supply processor designers with higher transistor densities and therefore chip area for additional logic. As instruction-level parallelism was already well exploited, computer architects started putting multiple cores onto a single chip.

The resulting homogeneous multicore architectures included multiple copies of the same complex core that had before powered a single-core processor. However, programs could not exploit the added computational resources of such multicore processors as easily as before. It now became necessary to write parallel programs that distribute their workload across multiple cores.

Once an application splits its work into separate tasks, it quickly becomes clear that not every task requires the same hardware capabilities. For example, for some tasks, the speedup obtained by exploiting instruction-level parallelism on the hardware level is not worth the added hardware complexity. Here, it can be more beneficial to spend the chip area to provide multiple simple cores instead of a single complex core. These simpler cores are still able to run the same code (i.e., they support the same instruction set), but trade sequential execution speed for a smaller area footprint, enabling more parallelism. Hence, such heterogeneous architectures offer different types of cores suitable for different types of tasks.

There can be different degrees of heterogeneity in an architecture. Offering cores with the same instruction set able to execute the same programs is the lowest degree of heterogeneity. Taking this idea further, some architectures provide completely different and specialized cores. These specialized cores may use different instruction sets and may not even be able to run general-purpose programs. However, they can provide superior throughput or energy efficiency for certain parallel tasks.

Hence, one dimension to modern parallel architectures is their core diversification: they not only incorporate many cores, but may also provide cores with different performance characteristics or even instruction sets. Some cores are small and highly specialized, but excel at energy efficiency or throughput for parallel workloads. Other cores are big and complex, but execute sequential program parts with high speed. The resulting heterogeneous multicore architectures provide vast computational resources in principle.

At the same time, there is a second dimension to the developments in the context of modern hardware architectures: the memory hierarchy. Single-core processors had a simple memory structure, where a single memory supplied data to the single core. To hide memory access latency and exploit spatial as well as temporal locality of memory accesses, these architectures included one or multiple levels of caches between core and memory.

Early multicore systems continued to use a single memory. Here, the hardware provides a shared physical address space. All cores can load and store values to that address space, which is backed by the single memory. To reduce access frequency to the main memory, architectures often also include per-core private caches. However, giving each of the cores in such a multicore system its own cache created a new problem: the possibility of accessing stale data due to outdated data copies in caches. If core  $c_1$  has a copy of some data item in its cache and another core  $c_2$  changes that data item in the main memory, core  $c_1$  now has a stale copy of that item in its cache. If  $c_1$  is not notified in some way, it will operate on an out-of-date copy; we say that the situation has become *incoherent*. In order to prevent such incoherent situations, multicore designs settled on implementing hardware-based protocols to keep caches coherent. These protocols thus make caches as functionally invisible as caches in a single-core system [SHW11].

In multicore systems with a single memory, memory access is uniform because distance, and therefore latency, to the memory is the same for every core in the system. As the number of cores further increased, soon a single memory was not able to satisfy the bandwidth requirements by the higher number of cores any more. Therefore, computer architects introduced physically distributed memory, i.e., multiple memories, while still providing a shared address space. This added a notion of locality: from the view of a particular core, there was now a notion of "local" and "remote" memory, with local memory being physically closer and offering, in general, lower access latency and higher bandwidth. Therefore, these systems are also known as non-uniform memory architectures. Their non-uniformity created new challenges. Suddenly, it mattered where data is placed in the memory and it can even be beneficial to copy data to more local memory to avoid frequent more expensive remote accesses.

4 1. Introduction

However, the increasing number of cores and the existence of distributed memory made it more difficult to keep caches coherent. Distributed memory is often used in conjunction with more complicated interconnects between cores, making the implementation of hardware-based coherence protocols considerably more complex. Additionally, overhead related to coherence often grows superlinearly with the number of cores [Kum+11]. This "coherence wall" [Kum+11] has led to the design of non-cache-coherent shared-memory architectures. These architectures still provide a shared address space for all cores in the system; however, they do not guarantee coherent caches on a hardware level. Thus, they remove a major factor that may limit scalability to higher core counts. Yet, caches are now not functionally invisible any more. Therefore, the software, on some level, needs to be aware of the caches and may have to manage coherence itself.

Alternatively, instead of offering a shared physical address space without hardware-based cache coherence, it is also possible to give up the shared address space altogether. Such architectures offer separate physical address spaces, i.e., there are memory locations that are only accessible by a subset of all cores in the system. Hence, such architectures require copying data between memories in order to make it accessible to cores associated with distinct address spaces.

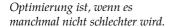

In summary, we have identified two important dimensions of heterogeneous parallel architectures: cores and memory. Figure 1.1 shows the design space spanned by these two dimensions with the characteristics we identified for each. We see a variety of cores, ranging from complex cores, well suited to execute sequential parts of a program by exploiting instruction-level parallelism, to simpler and highly specialized cores that provide higher integration density. Regarding the memory dimension, as we move to the right, we see that the hardware gradually relaxes guarantees to improve scalability. In general, moving up and right in this design space offers higher energy efficiency and more parallelism.

For both dimensions, the compiler plays a key role in the efficient usage of such heterogeneous multicore platforms. Regarding the core diversity, the compiler needs to generate code tailored to the respective core's capabilities. While complex cores extract some parallelism automatically on the hardware level, code generation is still challenging. Due to their

**Figure 1.1:** A possible design space of modern parallel hardware architectures. Depiction based on Sutter [Sut12].

complicated microarchitecture and execution behavior, deriving cost models to guide compiler code generation is difficult. Furthermore, large instruction sets significantly increase the number of possible encodings for constructs in the source program. In contrast, simpler cores have more predictable performance characteristics. However, they are more dependent on the compiler generating good code in the first place.

Regarding the memory architecture, the compiler must efficiently map the parallel programming model used by an application to the hardware. Due to relaxed hardware guarantees, the compiler may need to do additional work to bridge the gap between guarantees expected by the programmer and those actually provided by the hardware. Moreover, a more complicated memory structure may lead to the usage of different programming models, creating new optimization challenges.

6 1. Introduction

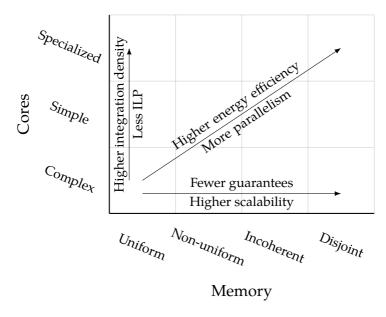

**Figure 1.2:** The point in the design space of modern parallel architectures targeted by compilation techniques presented in this dissertation. We make contributions in both dimensions.

#### 1.1. Contributions

This dissertation investigates compilation and code-generation techniques for modern parallel architectures. Figure 1.2 shows the point targeted by this dissertation in the architecture design space that we identified in the previous section. This dissertation makes contributions along both axes. More specifically, we investigate

- 1. compilation to invasive architectures, a familiy of non-cache-coherent shared-memory architectures; and

- 2. code generation in the context of out-of-order processors.

We give a brief introduction to each topic, before we state our technical contributions.

1.1. Contributions 7

**Non-cache-coherent shared memory.** Shared-memory architectures offer a single shared address space. Here, cores communicate by reading from and writing to a shared address space. These systems usually add caches to hide memory latencies and reduce memory traffic by exploiting temporal and spatial locality of data. However, caches create the potential for incoherent situations, i.e., the possibility of accessing stale data.

The standard solution to prevent incoherence is to implement a hardware cache coherence protocol to keep caches coherent. Simple coherence protocols do not scale well with increasing core count. While more complex protocols scale better, they may cause complexity and power issues. This scalability problem is known as the "coherence wall" [Kum+11].

Non-cache-coherent architectures represent a radical solution to circumvent the coherence wall. These architectures do not provide hardware-based cache coherence between all caches of the system. This raises the question of how to program such machines.

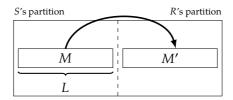

One possibility is to logically partition the address space. Thus, every coherence domain only accesses (and caches) addresses in its own partition, which sidesteps the issues caused by missing hardware-based coherence. However, this requires different programming models, such as the Partitioned Global Address Space (PGAS) model or the message-passing model. In both models, efficient data transfers between coherence domains are essential for program performance.

In this dissertation, we make the following technical contributions:

- We study the compilation of X10, a PGAS language, to invasive architectures, a family of non-cache-coherent architectures.

- We describe how we map X10's language features to invasive software and hardware.

- We study in detail data transfers on invasive architectures.

- We present a novel data-transfer technique that avoids serialization of pointered data structures.

- We propose hardware support for range-based cache operations and consider possible implementations.

- We extensively evaluate our data-transfer techniques on an FPGA prototype of an invasive architecture using an existing testsuite.

- We evaluate the hardware overhead of our range operations with an FPGA-based prototype implementation.

8 1. Introduction

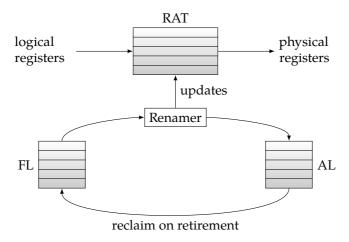

**Code generation with permutation instructions.** Modern parallel architectures exploit parallelism also on the instruction level. Such out-of-order processors dynamically rearrange instruction streams to the extent permitted by the data dependencies between instructions. Hence, instructions are not necessarily executed in the order specified in the program.

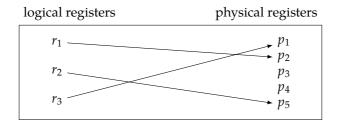

In order to implement this technique, such processors employ register renaming. Here, the processor has more physical registers than logical registers exposed in its instruction set. This enables the processor to eliminate certain dependencies between instructions, which would otherwise prevent their independent execution.

In a common implementation of register renaming, the processor contains a so-called register alias table. This table maps logical to physical registers. The table is purely controlled by hardware and inaccessible to software. We can express some value transfers between registers solely by modifying this indirection table, without touching any register contents.

There are many occasions during code generation where it would be beneficial for the compiler to have access to this mapping. However, current instruction sets only offer indirect access in the form of copy and swap instructions on registers.

In this dissertation, we make the following technical contributions:

- We propose the concept of permutation instructions that allow permuting the contents of a small set of registers. This can be viewed as allowing software to more directly manipulate an indirection table similar to a register alias table.

- We extend an existing instruction set with permutation instructions to arbitrarily permute up to five registers in one clock cycle.

- We describe an FPGA-based prototype implementation of this extended architecture with permutation instructions.

- We develop two code-generation schemes that allow compilers to exploit permutation instructions: a fast heuristic and an optimal dynamic programming-based approach.

- We formally prove the latter to be optimal.

- We implement both code-generation schemes in an existing compiler and conduct an extensive evaluation using an adapted processor emulator as well as our hardware prototype.

1.2. Structure

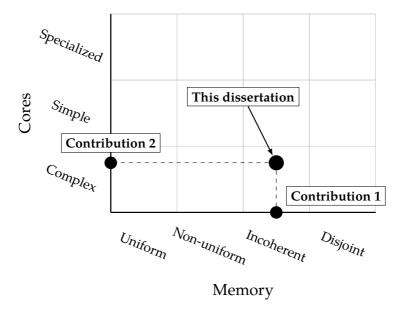

**Figure 1.3:** The structure of this dissertation.

#### 1.2. Structure

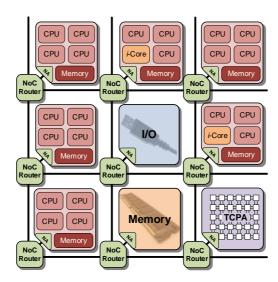

In Chapter 2, we first give an overview of non-cache-coherent architectures and discuss their impact on programming models and compilers. This allows us to proceed to Chapter 3, which introduces the research project Invasive Computing, as part of which we carried out the work described in this dissertation. In particular, we present the hardware platform developed in the context of this project as an instance of a heterogeneous non-cache-coherent shared-memory architecture using our groundwork from Chapter 2. This hardware platform serves as the basis for both our contributions.

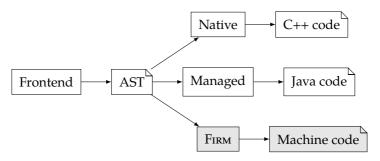

Then, in Chapter 4, we discuss compilation of X10 to invasive architectures. This includes our contribution regarding the efficient copying of pointered data structures.

Subsequently, we turn towards code generation aspects in Chapter 5. Here, we present our contribution concerning the use of permutation instructions to speed up program execution. To increase locality, we introduce the necessary hardware basics at the beginning of this chapter.

Chapter 6 summarizes our results and presents ideas for future research.

10 1. Introduction

#### 1.3. Notation and Conventions

As the results presented in this dissertation are intimately connected with several research projects that have many contributors, this dissertation uses "we" everywhere (except for the acknowledgment section). For the sake of completeness, we include some material that is not the contribution of the author. We explicitly state this fact at the beginning of such sections and switch to "Contributor et al." and "they" if necessary.

We finish our definitions and theorems with a non-filled square □ and our proofs with a black square ■. We typeset code like this, with keywords such as **if** and **else** highlighted bold. We add hyphens to compound words if it avoids ambiguities. We use a comma after both "e.g." and "i.e.", as proposed by the majority of style guides we consulted. We differentiate between running time (the wall clock time of benchmark runs), run-time (the point in time when a program runs, in contrast to, e.g., compilation time), and runtime (as a shorthand for runtime library). We use the units and prefixes defined by the standard IEEE 1541-2002.

In printed versions of this dissertation, we provide a DVD with all software artifacts produced as part of this dissertation. We also make all artifacts available for download. See Appendix B for an overview. All specific software revisions we mention are relative to the projects listed there.

#### 1.4. List of Publications

In this section, we give an overview of the author's publications. We differentiate between publications that contribute to the dissertation at hand and those which do not.

The following publications contribute to material presented in this dissertation. All mentioned talks were given by the author.

Manuel Mohr, Artjom Grudnitsky, Tobias Modschiedler, Lars Bauer, Sebastian Hack, and Jörg Henkel. "Hardware Acceleration for Programs in SSA Form". In: *International Conference on Compilers, Architecture and Synthesis for Embedded Systems*. CASES'13. Piscataway, NJ, USA: IEEE Press, 2013, 14:1–14:10. DOI: 10.1109/CASES.2013.6662518

Presented on October 1, 2013 in Montréal, Canada.

Matthias Braun, Sebastian Buchwald, Manuel Mohr, and Andreas Zwinkau. *Dynamic X10: Resource-Aware Programming for Higher Efficiency*. Tech. rep. 8. X10 '14. Karlsruhe Institute of Technology, 2014. URL: http://digbib.ubka.uni-karlsruhe.de/volltexte/1000041061

Presented on June 12, 2014 in Edinburgh, Scotland.

Manuel Mohr, Sebastian Buchwald, Andreas Zwinkau, Christoph Erhardt, Benjamin Oechslein, Jens Schedel, and Daniel Lohmann. "Cutting out the Middleman: OS-Level Support for X10 Activities". In: *Proceedings of the ACM SIGPLAN Workshop on X10*. X10′15. Portland, OR, USA: ACM, 2015, pp. 13–18. ISBN: 978-1-4503-3586-7. DOI: 10.1145/2771774.2771775

Presented on June 14, 2015 in Portland, USA.

Sebastian Buchwald, Manuel Mohr, and Ignaz Rutter. "Optimal Shuffle Code with Permutation Instructions". In: *Algorithms and Data Structures*. Ed. by Frank Dehne, Jörg-Rüdiger Sack, and Ulrike Stege. Vol. 9214. WADS'15. Lecture Notes in Computer Science. Springer International Publishing, 2015, pp. 528–541. DOI: 10.1007/978-3-319-21840-3\_44 Sebastian Buchwald, Manuel Mohr, and Ignaz Rutter. "Optimal Shuffle Code with Permutation Instructions". In: *CoRR* abs/1504.07073 (2015). URL: http://arxiv.org/abs/1504.07073

Presented on August 5, 2015 in Victoria, Canada.

Manuel Mohr and Carsten Tradowsky. "Pegasus: Efficient Data Transfers for PGAS Languages on Non-Cache-Coherent Many-Cores". In: *Proceedings of Design, Automation and Test in Europe Conference Exhibition*. DATE'17. IEEE, Mar. 2017, pp. 1781–1786. DOI: 10.23919/DATE.2017.7927281

Presented on March 30, 2017 in Lausanne, Switzerland.

Matthias Braun, Sebastian Buchwald, Manuel Mohr, and Andreas Zwinkau. *An X10 Compiler for Invasive Architectures*. Tech. rep. 9. Karlsruhe Institute of Technology, 2012. URL: http://digbib.ubka.uni-karlsruhe.de/volltexte/1000028112

12 1. Introduction

The following publications do not contribute to material presented in this dissertation.

Jonathan Aldrich, Ronald Garcia, Mark Hahnenberg, Manuel Mohr, Karl Naden, Darpan Saini, Sven Stork, Joshua Sunshine, Éric Tanter, and Roger Wolff. "Permission-Based Programming Languages (NIER track)". In: *Proceedings of the 33rd International Conference on Software Engineering*. ICSE '11. New York, NY, USA: ACM, 2011, pp. 828–831. DOI: 10.1145/1985793.1985915

Sven Stork, Karl Naden, Joshua Sunshine, Manuel Mohr, Alcides Fonseca, Paulo Marques, and Jonathan Aldrich. "AEminium: A Permission Based Concurrent-by-Default Programming Language Approach". In: *ACM Transactions on Programming Languages and Systems*. TOPLAS 36.1 (Mar. 2014), 2:1–2:42. DOI: 10.1145/2543920

Sebastian Buchwald, Manuel Mohr, and Andreas Zwinkau. "Malleable Invasive Applications". In: *Proceedings of the 8th Working Conference on Programming Languages*. ATPS'15. Springer Berlin Heidelberg, 2015, pp. 123–126

Alexander Pöppl, Marvin Damschen, Florian Schmaus, Andreas Fried, Manuel Mohr, Matthias Blankertz, Lars Bauer, Jörg Henkel, Wolfgang Schröder-Preikschat, and Michael Bader. "Shallow Water Waves on a Deep Technology Stack: Accelerating a Finite Volume Tsunami Model using Reconfigurable Hardware in Invasive Computing". In: *Euro-Par 2017: Parallel Processing Workshops*. Lecture Notes in Computer Science. Heidelberg, Berlin: Springer-Verlag, Aug. 2017

There are only two hard things in Computer Science: naming things, cache invalidation, and off-by-1 errors.

Leon Bambrick, based on quote by Phil Karlton

2

#### **Non-Cache-Coherent Architectures**

In this chapter, we give an overview of non-cache-coherent shared-memory architectures. First, we cover fundamentals about parallel hardware architectures. Then, we give a more precise definition of cache coherence and present hardware-based and software-based implementation techniques. Subsequently, we discuss reasons for abandoning hardware-based coherence and give examples of resulting architectures. Lastly, we investigate the impact of missing hardware-based coherence on programming models and compilers.

# 2.1. A Taxonomy of Parallel Architectures

In this section, we give an overview of different types of parallel hardware architectures. We base our presentation on [HP11], but deviate in some details. We look at two orthogonal aspects:

- 1. How is memory organized?

- 2. How do cores communicate?

#### 2.1.1. Memory Organization

We differentiate between architectures with centralized and distributed memory.

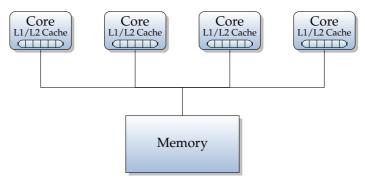

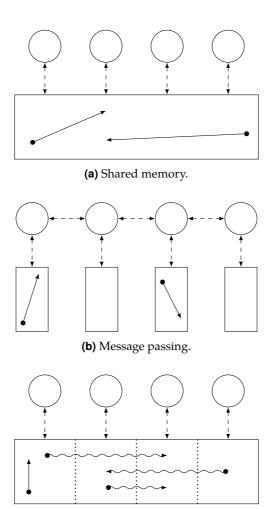

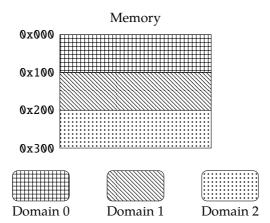

**Centralized memory.** Figure 2.1a shows the basic structure of machines with a centralized memory. Following this model, one or more cores share a single memory. Typically, the cores are connected to the memory via a bus. When adding more and more cores to such an architecture, the memory becomes a bottleneck as it cannot satisfy the bandwidth requirements of a large number of cores. While larger caches can mitigate this effect, past a certain core count it becomes necessary to have multiple memories.

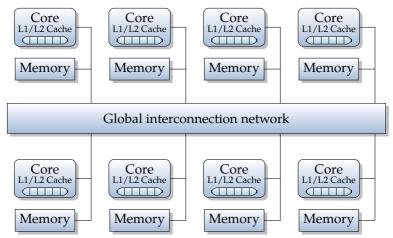

**Distributed memory.** Figure 2.1b shows the basic structure of such systems with a physically distributed memory, i.e., multiple memories. Each core or group of cores has a local memory and all cores are connected by a scalable global interconnection network. The main advantage of distributed-memory machines is that multiple memories also multiply the possible memory bandwidth, i.e., it is easier to supply enough data to all cores than with a single memory. Distributed memory has the main disadvantage of higher implementation complexity, especially for the global interconnection network, which must be able to support the higher available memory bandwidth.

#### 2.1.2. Communication Model

We differentiate between communication via shared memory and via message passing.

**Shared memory.** In a shared-memory system, the hardware offers a single shared address space. Each core may read from and write to this address space. Hence, cores can communicate via loads and stores to the shared address space.

**(a)** A centralized memory architecture. In this case, four cores are connected to a single main memory by a bus.

**(b)** A distributed-memory architecture. Eight cores, each connected to a local memory, are connected via a global interconnect.

**Figure 2.1:** A comparison of memory architectures.

**Message passing.** In a pure message-passing system, the hardware does not offer a shared address space. Hence, it is not assumed that every core can access all available memory. Thus, in general, cores cannot share data and therefore communicate by sending explicit messages. Passing a message is inherently linked to copying the necessary data to the receiver's address space as otherwise the receiver is unable to access the data.

# 2.1.3. Typical Combinations

In theory, memory organization and communication model are completely independent. In practice, the following three combinations are important.

**Shared memory with centralized memory.** Machines that provide shared memory with a single centralized memory are often called *symmetric multiprocessing* (*SMP*) systems. As all cores have the same distance from the single main memory, they also have the same access latency. Therefore, these machines are also called *uniform memory access* (*UMA*) architectures. This is the most popular type of memory organization for single-core and multi-core machines.

**Shared memory with distributed memory.** Machines that provide shared memory with distributed memory are usually referred to as *distributed shared-memory* (*DSM*) architectures. Here, the hardware still provides a single address space, hence every core can still access the complete memory. However, there is now a notion of locality as accessing a local memory is faster than accessing a remote memory. Therefore, these machines are also called *non-uniform memory access* (*NUMA*) architectures. The NUMA model is the standard for today's server machines. Typically, this is due to the memory controller being integrated into the processor. Hence, as soon as a machine possesses multiple physical processors, i.e., CPUs in multiple sockets, it automatically becomes a NUMA architecture.

**Message passing with distributed memory.** Such machines typically provide multiple private address spaces. Each core or group of cores has its own private address space, which is not addressable by remote cores.

Hence, the same physical address can refer to different memory locations for different cores. A typical representative of this class of machines is a cluster computer. Often, clusters are not pure message-passing systems. For efficiency reasons, shared memory is offered and used for small groups of cores, e.g., one node of a cluster, and message passing is used between core groups.

#### 2.2. Cache Coherence

Usually, systems introduce caches to exploit spatial and temporal locality of data accesses. Typically, every memory address accessed by a core is first looked up in the core's cache. For example, when a core loads from memory address A, it is first checked if there is a valid copy of the data from A in the cache. This is called a *cache hit*, where the cache returns the value from the local data copy without consulting the memory. Only in case of a *cache miss* is the memory actually accessed.

In a shared-memory system with multiple cores, the caching of data can lead to *incoherent* situations unless special measures are taken. In general, incoherence refers to a situation where stale, i.e., outdated, data is accessed. As an example, suppose that we have two cores  $c_1$  and  $c_2$ , each with a private cache. Further, suppose that the shared memory holds the value 100 at address A. First, both cores read from A and therefore have copies of that datum (100) in their local caches. Now,  $c_1$  writes the value 200 to A. After the write by  $c_1$ ,  $c_2$  reads from A. If we do not take any precautions, the situation has now become incoherent, as  $c_2$  would still read the old value 100 from its cache.

In practice, this incoherent situation is prevented by using a coherence protocol. In our example, this protocol must prevent  $c_2$  from observing the old value while  $c_1$  observes the new value. There exist numerous possible protocol variants and even more implementation possibilities, but all protocols have in common that they maintain *coherence invariants*. To understand what a coherence protocol must accomplish, first we have to define coherence in a precise manner.

We follow the definition by Sorin et al. [SHW11, section 2.3]. Sorin et al. use the *single-writer-multiple-reader* (SWMR) *invariant* as the foundation for their definition of coherence. The SWMR invariant states that, for any given memory location M at any given moment in time, there is

- (i) either a single core that may read and write M, or

- (ii) any number of cores that may only read *M*.

Especially, there must not exist a point in time, so that some memory location M may be written by a core and at the same time read or written by another core.

Sorin et al. propose another way of viewing this definition. They divide the lifetime of each memory location into *epochs*. Viewed this way, during each epoch there must be either a single core with read-write access or any number of cores with read-only access.

However, the SWMR invariant alone is not enough to capture our intuitive understanding of coherence. For example, in an epoch where two cores have read access to a memory location, the SWMR invariant does not state anything about the values that the cores read. Hence, it would be allowed that they read different values. Clearly, this is an incoherent situation like the one from our first example and therefore we must complement the SWMR invariant.

Sorin et al. add the *data-value invariant*. This invariant regulates the propagation of values from one epoch to the next. More precisely, it states that the value of a memory location M at the start of an epoch is the same as the value of M at the end of M's last read-write epoch.

**Definition 1** We call a system *coherent* if the following two invariants hold [SHW11, p. 13]:

- 1. Single-Writer, Multiple-Reader (SWMR) Invariant: For any memory location M, at any given (logical) time, there is only a single core that may write to M (and can also read it), or any number of cores (possibly zero) that may only read M.

- 2. Data-Value Invariant: The value of a memory location M at the start of an epoch is the same as the value of M at the end of M's last read-write epoch.

2.2. Cache Coherence

| Core $c_1$ :                                                    | Core $c_2$ :                                                    |  |

|-----------------------------------------------------------------|-----------------------------------------------------------------|--|

| $S_1: \mathbf{x} \leftarrow 1$ $L_1: r_1 \leftarrow \mathbf{y}$ | $S_2: \mathbf{y} \leftarrow 1$ $L_2: r_2 \leftarrow \mathbf{x}$ |  |

**Figure 2.2:** Program running on two cores. Initially, memory locations  $\mathbf{x}$  and  $\mathbf{y}$  hold the value 0.

#### 2.2.1. Separating Coherence from Consistency

Following Sorin et al. [SHW11], we separate the issue of coherence from the issue of memory consistency. A memory-consistency model, or memory model for short, specifies the allowed behavior of a system where multiple cores execute loads and stores on a shared memory. For a given program, program input, and initial memory state, the memory model specifies what values the load operations executed by a core may return, and the memory model defines a final memory state.

Viewed another way, if we look at the set *E* of all possible executions for a given program, a memory model partitions *E* into a set of allowed executions (that adhere to the rules of the model) and a set of disallowed executions (that do not adhere to the model's rules). In contrast to execution on a single core, with multiple participating cores a memory model usually allows multiple correct program executions and disallows many incorrect executions.

Figure 2.2 shows an example program inspired by Dekker's algorithm [Dij02] for mutual exclusion. We use  $\mathbf{x}$  and  $\mathbf{y}$  to denote memory locations, use  $r_i$  for machine registers, and use  $L_j$  and  $S_k$  for load and store operations, respectively. Initially, memory locations  $\mathbf{x}$  and  $\mathbf{y}$  hold the value 0. In the program, core  $c_1$  writes 1 to  $\mathbf{x}$  and then reads from  $\mathbf{y}$  into a local register. Similarly, core  $c_2$  writes 1 to  $\mathbf{y}$  and then reads from  $\mathbf{x}$  into a local register.

Now, which outcomes of this program are allowed? Intuitively,  $(r_1, r_2) = (1, 1)$ ,  $(r_1, r_2) = (0, 1)$ , and  $(r_1, r_2) = (1, 0)$  are possible due to different interleavings of the instructions. These outcomes are *sequentially consistent* as the interleavings respect the partial orders defined by the program order of instructions in each sequential program part.

| $c_1$       | $c_2$       | coherence state of x                                                                       | coherence state of y                                                                      |

|-------------|-------------|--------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|

| $L_1$ $S_1$ | $L_2$ $S_2$ | read-only for noone<br>read-only for $c_2$<br>read-write for $c_1$<br>read-write for $c_1$ | read-only for $c_1$<br>read-only for $c_1$<br>read-only for $c_1$<br>read-write for $c_2$ |

**Table 2.1:** Coherence states for the execution  $L_1$ ,  $L_2$ ,  $S_1$ ,  $S_2$  of the program from Figure 2.2.

But what about an outcome where both cores load the value 0, i.e.,  $r_1 = 0$  and  $r_2 = 0$  after execution of the program? A first intuition could be that this can only happen due to some coherence-related problem, where the system is incoherent and the cores read stale, i.e., not updated yet, values of x and y.

Indeed, a faulty coherence mechanism could lead to this situation. Suppose the writes from both cores are cached in the core's respective caches. Now, assuming a faulty coherence implementation, the following reads by both cores could load 0, i.e., stale values. This would violate the data-value invariant of Definition 1.

However, as we see in the following, there is an execution order that conforms to our definition of coherence and at the same time leads to the observed program behavior. Table 2.1 shows the coherence states of memory locations  $\mathbf{x}$  and  $\mathbf{y}$  during the execution  $L_1$ ,  $L_2$ ,  $S_1$ ,  $S_2$ . We see that neither of our invariants from Definition 1 is violated, hence, this execution is coherent.

It may seem strange that load and store operations are executed in an order different from the program order. Perhaps suprisingly, even common memory models, including the Java memory model and the x86 memory model, allow this execution order<sup>2</sup>. The reason for this is that allowing such executions enables a multitude of performance optimizations, both on the software level, i.e., in the compiler or virtual machine, and on the hardware level.

<sup>&</sup>lt;sup>2</sup>Modern memory models guarantee sequential consistency for data-race-free programs (the so-called DRF guarantee). However, our example program contains a data race.

2.2. Cache Coherence 21

For example, if a compiler can prove that x and y from Figure 2.2 do not alias, i.e., always refer to distinct memory locations, the compiler is allowed to generate code that first loads a value and then stores the other, even if in the program the write precedes the read<sup>3</sup>. Similarly, the CPU cache may include write buffers to hold data that must be written to memory. The buffer enables the cache to service following load operations without waiting for the memory to actually finish writing back the value of the store operation, effectively allowing a load to overtake a preceding store.

Hence, it is useful to separate the concepts of cache coherence and memory consistency. Sorin et al. give two more reasons why these are two separate issues. First, an important difference between coherence and consistency is that coherence is only concerned with a single memory location, while memory-consistency models consider accesses to multiple memory locations. This is also apparent in Definition 1, which only deals with accesses by multiple cores to a single memory location. And second, the question of whether the discussed execution of the program from Figure 2.2 is allowed also arises in a system without any caches. In such a system, there is clearly no need for cache coherence; however, it still needs a memory model. In practice, most implementations of memory models assume and exploit cache coherence.

#### 2.2.2. Implementation

Definition 1 tells us what a coherence protocol must achieve but not how it can maintain these invariants. Again, we have orthogonal design decisions: we can choose between different coherence policies; we can choose a granularity; and we can put the responsibility for implementing coherence onto hardware or software.

The implementation of a coherence protocol often depends on the cache configuration. We can configure caches in *write-through* or *write-back* mode. Write-through caches update the main memory on every write. Hence, the main memory always contains an up-to-date value for a certain

<sup>&</sup>lt;sup>3</sup>All modern programming languages that define a memory model offer means to restrict such reorderings, e.g., by using the keyword volatile [Gos+14, section 17.4] in Java.

address. Write-back caches do not update the main memory on every write. Therefore, with multiple write-back caches, it is more difficult to find the most up-to-date value of a data item, as it can be solely located in one of the caches. In such a case, cache terminology usually refers to this copy as *dirty*. In general, write-through caches are simpler to implement but have higher main-memory-bandwidth requirements.

#### 2.2.2.1. Coherence Policy

In general, we can classify a coherence policy as either *write-invalidate* or *write-update* [Ste90; PP84]. Both types of policies must maintain the invariants from Definition 1.

Write-invalidate policies maintain coherence as follows. When a core c updates its local data copy of memory location L, write-invalidate policies enforce the invalidation of all other copies of L. Hence, the SWMR invariant is maintained by forcing the coherence state of L to "read-write for c". The next time another core c" reads L, either c provides the new value directly to c", or c first writes back its local value to memory location L, where c" then fetches it from.

With a write-update policy, when a core updates its local data copy of memory location L, at the same time, it updates all other copies of L. Hence, the SWMR invariant is maintained by forcing the coherence state of L directly to "read-only for all cores that had a copy of L". The policy implementation decides whether the copy in memory is updated as well.

Write-invalidate policies distribute updated data items lazily, while write-update policies do so eagerly. In general, write-invalidate policies are far more common than write-update policies.

#### 2.2.2.2. Granularity

Common processors can perform loads and stores at various granularities, usually ranging at least from 1 to 8 bytes, and sometimes including wide memory operations, e.g., 64 bytes for vector instructions. In theory, it would be possible to manage coherence at the finest granularity, i.e., 1 byte.

However, this would considerably increase overhead for implementation and coherence traffic.

Therefore, in practice, implementations manage coherence at a coarser granularity, most commonly cache lines. Enforcing the coherence invariants per cache line is, in general, more efficient, as they comprise multiple bytes (16–64 bytes are common). However, managing coherence at a coarse granularity can also cause other performance problems, such as false sharing [BS93].

False sharing occurs when multiple cores access and modify different, non-overlapping data objects within the same cache line. For example, suppose that core  $c_1$  repeatedly modifies memory location  $L_1$ , core  $c_2$  repeatedly modifies memory location  $L_2$  (different from  $L_1$ ), and  $L_1$  and  $L_2$  happen to be part of the same cache line. Here, the coherence protocol still maintains the SWMR invariant for the whole cache line. Hence, every time  $c_1$  modifies  $L_1$ , a coherence action is triggered. For example, assuming a write-invalidate protocol,  $c_2$ 's cache line containing  $L_2$  is invalidated, although  $L_2$  did not change at all. The same happens for  $c_1$ 's cache line containing a copy of  $L_1$  on the next update to  $L_2$  by  $c_2$ . Thus, an unfortunate combination of memory layout, access behavior, and coherence granularity can lower performance significantly.

#### 2.2.2.3. Responsibility

We can implement the system that maintains the coherence invariants either in hardware or in software [Adv+91; TM97].

**Hardware-based coherence.** If we implement coherence in hardware, it is functionally invisible to software. Hence, for a shared-memory system with hardware-based cache coherence, the caches behave like in a single-core system. Correctly implemented, hardware-based cache coherence makes it impossible for the programmer to determine whether a system has caches by inspecting the results of load and store operations [SHW11]. However, it may be possible to deduce the presence of caches using timing information.

In the following, we give a brief overview of the two most important implementation techniques for hardware-based cache coherence: snooping protocols and directory schemes. Snooping protocols rely on a medium that is able to broadcast information, e.g., a bus, and distribute the information about the sharing status of each memory block. On the other hand, directory schemes centralize the information about the sharing status of memory blocks in one location, called the directory. As a consequence, they do not require the ability to broadcast information. In general, snooping protocols are easy and cheap to implement, while directory schemes are more complex, but scale to higher core counts. We base our presentation on Hennessy et al.'s [HP11] and also refer to the same source for details.

The idea behind snooping protocols is that addresses are broadcast on the shared medium (e.g., a bus) and all participants observe, or "snoop", these addresses to potentially trigger actions in their respective local caches to maintain coherence [HP11, section 4.2]. To illustrate this idea, we discuss the implementation of a snooping coherence protocol for a simple memory architecture using a bus as shown in Figure 2.1a. We assume a write-invalidate policy, as it is the most commonly used strategy.

As an example, suppose we have two cores  $c_1$  and  $c_2$  in such a system, each with a private cache configured in write-back mode. If  $c_1$  reads from address L, it puts a copy of the data at address L in its local cache. Suppose  $c_2$  now wants to write a new value to L, which proceeds as follows. After  $c_2$  has successfully acquired bus access<sup>4</sup>, it broadcasts an invalidate operation on the bus. Core  $c_1$  reacts by invalidating its local copy of L, i.e., the next access to L by  $c_1$  will cause a cache miss. Then,  $c_2$  performs the actual write operation. With write-back caches, now only  $c_2$ 's cache holds the new value of L; the copy of L in  $c_1$ 's cache is marked invalid and the copy in memory is outdated.

If  $c_1$  now reads from L again, we must (i) somehow notice that reading from main memory is incorrect (as the new value is in  $c_2$ 's cache), and (ii) transport the new value to  $c_1$ 's cache. Fortunately, we can implement the notification mechanism exactly as with the original write described before. Thus, we require caches to also observe read operations on the

$<sup>^4</sup>$ If multiple cores want to write to the same address L concurrently, the bus-acquisition process serializes their write operations.

bus and to check if they have a modified copy of the data at the requested address. If this is the case, they abort the other core's memory access and then provide the new value. In our example,  $c_2$  would see  $c_1$ 's read to L on the bus and then abort it.

How exactly then  $c_2$  makes the new value available to  $c_1$  is another design decision. One option is that  $c_2$  writes back the new value to main memory and then sends a retry signal to  $c_1$ , which restarts the read operation. The alternative is that  $c_2$  sends the new value directly to  $c_1$ , without a detour via main memory. The first option is easier to implement but potentially slower as updated values are distributed via main memory. The second option requires additional bookkeeping and increases implementation complexity, but distributes updated values over a potentially faster interconnect between cores, without involving main memory. This design decision differentiates the two well-known coherence protocols MESI [PP84] and MOESI [Adv10, section 7.3].

As we have seen, bus snooping protocols need to broadcast, i.e., communicate with all other caches, on every cache miss. On a read miss, we have to inform all other caches of our intent to read the address and they might respond by aborting our read request, followed by providing the updated data item. On a write miss, we also have to inform all other caches as they might need to invalidate their copy. In total, the amount of coherence-related traffic can soon overwhelm the capabilities of the bus as we increase the number of cores (and caches).

An alternative offering better scalability are directory protocols [HP11, section 4.4]. They build upon the idea of the *directory*, which is a data structure that holds the sharing status of each cacheable memory block. The most important improvement compared to snooping-based protocols is that we save the sharing status of a block in a single, well-defined location (the directory) instead of replicating information in multiple locations. This avoids the need to broadcast information to synchronize multiple copies of the sharing status.

However, we can still distribute the directory itself. Directory schemes are often used for distributed shared-memory machines as depicted in Figure 2.1b. In such a setting, each core with its local cache and local memory is extended with a directory responsible for the memory blocks in the respective local memory. Hence, while the sharing information is

distributed, it is not replicated, as we save the current sharing status of each memory block in exactly one location.

In their simplest form, directory schemes maintain one directory entry per memory block. Each entry holds the block's current sharing status. A basic protocol differentiates between the following sharing states (with more fine-grained states allowing potentially higher performance at the cost of increased complexity):

**Uncached:** No core has a copy of the memory block.

**Shared:** The block is cached by at least one core, and the values of this block in memory and in all caches match. This means no core has modified the block. Additionally, we have to save information about which cores have copies of the block in their caches (the *sharer set*).

**Modified:** Exactly one core (the owner) has a copy of the block, and the block is modified. Hence, the copy in memory is outdated. We also save which core is the owner.

In a directory scheme, up to three types of cores may be involved in a memory access:

- the local requesting core that reads or writes the cache block;

- the home core whose memory holds the requested cache block; and

- the remote core whose cache holds a copy of the requested cache block.

As an example, suppose we have three cores  $c_1$ ,  $c_2$ , and  $c_3$  in a DSM system as shown in Figure 2.1b, each with private write-back caches. We assume that initially, all caches are empty, i.e., all entries in all directories are set to Uncached. Furthermore, we assume memory location L is physically located in  $c_1$ 's memory.

Now, suppose that in our example  $c_1$  reads from L. Here,  $c_1$  is both the local and the home core; no remote core is involved as all caches are empty. Hence,  $c_1$  puts L in its local cache and updates in its local directory the state of L to Shared as well as the respective sharer set to  $\{c_1\}$ .

Now, assume that  $c_2$  reads L next. The local core  $c_2$  then sends a read request to home core  $c_1$ , which adds core 2 to the set of sharers registered for L in  $c_1$ 's directory, and then returns the data at L to  $c_2$ .

Now, suppose that the next action is a write to L by  $c_3$ . Hence, the local core  $c_3$  sends a write request to home core  $c_1$ . Core  $c_1$  responds by (i) sending the requested block back to  $c_3$ , (ii) reading the set  $\{c_1, c_2\}$  of sharers and sending them invalidation requests, and (iii) setting the state of L to Modified in  $c_1$ 's directory while registering  $c_3$  as the owner. Cores  $c_1$  and  $c_2$  then invalidate their local copies of L.

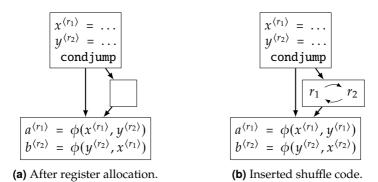

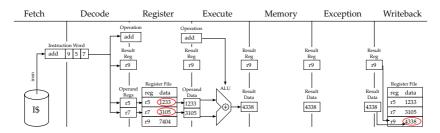

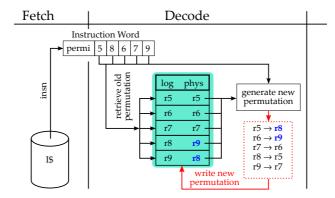

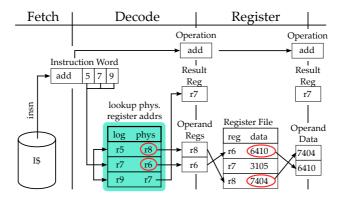

In summary, directory schemes scale better than snooping-based protocols as they do not depend on broadcasts. However, they are also difficult to scale to large numbers of cores. For example, the sharer set is often implemented as a bit set with one bit per core, where a 1 at position i means that core  $c_i$  currently has a copy of the respective memory location in its cache. For 1024 cores, storing the bit set requires 128 bytes, which may be more than the size of the memory block whose sharing state the bit set is supposed to track. Another issue is the significantly increased power usage due to the high number of messages for coherence traffic [KK10].